Seri 4000 diperkenalkan sebagai CD4000 COS/MOS tahun 1968 oleh RCA sebagai daya yg lebih rendah serta alternatif yg lebih serbaguna untuk seri 7400 chip Transistor-Transistor Logic (TTL).

Karakteristik 4000 Seri CMOS IC

Supply: 3 hingga 15V, Fluktuasi kecil ditoleransi.

Tidak akan mempengaruhi bab sirkuit di mana terhubung. Bahwa input yg tidak tersambung sanggup menangkap gangguan listrik serta berubah dengan cepat antara bab tinggi serta rendah yg tidak sanggup diprediksi.

Output: Dapat karam serta sumber sekitar 1mA.

Jika mempertahankan tegangan output untuk menggerakkan input CMOS.

Jika tidak perlu menggerakkan input, Arus maksimum (5mA) pasokan 6V, atau (10mA) pasokan 9V (cukup untuk menyalakan LED).

Fan-Out: Satu output sanggup mendorong hingga 50 input.Waktu perambatan gerbang: Biasanya 30ns

Untuk sinyal melaksanakan perjalanan melalui gerbang dengan suplai 9V, diharapkan waktu yg lebih usang pada tegangan suplai yg lebih rendah.

Frekuensi: Hingga 1MHz

Di atas seri 74 ialah pilihan yg makin bagus. Konsumsi Daya sangat rendah, beberapa µW. Jauh lebih besar pada frekuensi tinggi, beberapa mW pada 1MHz.

Static Precautions

CMOS IC Seri 4000 bersifat Statis Sensitif

Menyentuh pin dikala diisi dengan Listrik Statis sanggup merusak IC.

Kebanyakan IC dalam penggunaan cukup toleran serta membumikan tangan dengan menyentuh pipa air metal atau bingkai jendela sebelum menangani.

IC harus dibiarkan dalam kemasan pelindung hingga siap menggunakannya.

1Hz Quartz Oscillator

Basis waktu 1 Hz untuk jam digital, pengatur waktu. Jam mempunyai ketepatan yg luar biasa. Dibangun di sirkuit terpadu U1 (4060) serta U2 (4027), Kristal 32,768KHz, beberapa Resistor serta Kapasitor.

U1 ialah Counter Ripple Binary 14-bit serta mempunyai osilator internal. Osilator berjalan pada 32.768KHz. Pin-3, Sinyal Clock 2Hz, yg berasal dari sinyal Osilator utama yg frekuensi dibagi dengan 214 (16384).

Sinyal 2Hz dilewatkan ke pin Input clock U2, merupakan Flip-Flop JK Ganda, serta Frekuensi dibagi 2. Output Q2 (Pin-1 dari U2) mendapat 1Hz.

Menggunakan kristal jenis kuarsa dengan Nilai Standar (32.768 KHz) yg dipakai dalam jam tangan elektronik. C2 dipakai untuk pembiasaan mikrometri dari frekuensi osilator, sehingga sanggup dikalibrasi sempurna untuk 32,768 KHz. Kalibrasi sanggup dilakukan dengan memakai pengukur frekuensi.

Generator sangat Stabil serta lebih akurat jenis generator jam sederhana lainnya. Stabilitasnya tergantung pada kualitas kristal serta pada perubahan suhu sekitar.

- Basic Logic Gate -

LOGIC Integrated Circuit

WikiPedia

CD4001 Quad 2 input NOR gate

CD4002 Dual 4 input NOR gate

CD4007 Dual comp pair plus inverter

CD4008 4 bit full adder

CD4009 Hex buffer / converter inverting

CD4010 Hex buffer / converter non-inverting

CD4011 Quad 2 input NAND gate

CD4012 Dual 4 input NAND gate

CD4013 Dual D-Type flip flop with set/reset

CD4015 Dual 4 stage static shift register

CD4016 Quad bilateral switch

CD4017 Decade counter

CD4018 Preset Divide ny N counter

CD4020 14 stage binary counter

CD4022 Octal counter

CD4023 Triple 3 input NAND gate

CD4024 7 stage binary counter

CD4025 Triple 3 input NOR gate

CD4026 Decade counter / divider

CD4027 Dual JK master - Slave flip flop

CD4028 BCD to decimal decoder

CD4030 Quad 2 input XOR gate

CD4033 Decade counter / divider

CD4035 4 stage PIPO shift register

CD4040 12 stage binary counter

CD4041 Quad true / compliment buffer

CD4042 Quad clocked D latch

CD4043 Quad 3 state R/S latch NOR

CD4044 Quad 3 state R/S latch NAND

CD4046 Phase locked loop

CD4047 Monostable / Astable multivibrator

CD4049 Hex buffer / converter inverting

CD4538 Dual precision monostable multivibrator

CD4543 BCD to 7 segment LCD driver

CD4555 Dual binary to 1 of 4 decoder

CD4556 Dual binary to 1 of 4 decoder

MC14557 Variable Length Shift Register

MC14584 Hex Schmitt Trigger

CD4050 Hex buffer / converter non-inverting

CD4051 8 channel MUX

CD4052 Differential 4 channel MUX

CD4053 Triple 2-channel analog multiplexer

CD4054 4 segment LCD driver

CD4055 BCD to 7 segment decoder / driver

CD4056 BCD to 7 segment decoder / driver

CD4059 Programmable divide by N counter

CD4060 14 stage ripple carry binary counter / divider

CD4063 4-bit comparator

CD4066 Quad bilateral switch

CD4068 8-input NAND/AND gate

CD4069 Hex inverter

CD4070 Quad 2 input XOR

CD4071 Quad 2 input OR

CD4072 Dual 4 input OR gate

CD4073 Triple 3 input AND gate

CD4075 Triple 3 input OR gate

CD4077 Quad 2 input XNOR gate

CD4081 Quad 2 input AND

CD4082 Dual 4 input AND gate

CD4089 Binary rate multiplier

CD4098 Dual monostable multivibrator

MC14469 Addressable UART

MC14495 BCD 70 &-seg latch/decoder/driver

CD4503 Hex buffer

CD4504 Hex voltage level shifter TTL-CMOS

CD4511 BCD to 7 segment latch decoder drivers

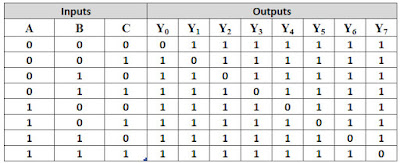

CD4514 4 bit latch / 4 to 16 line decoders

CD4515 4 bit latch / 4 to 16 line decoders

CD4518 Dual BCD up counter

CD4520 Dual binary up counter

[ Avionics Knowledge ] - [ The Computer Networking ]